2025/05/19 10:27 Telum II at Hot Chips 2024: Mainframe with a Unique Caching Strategy

ロボ子、IBMの新しいTelum IIプロセッサ、知ってるか?

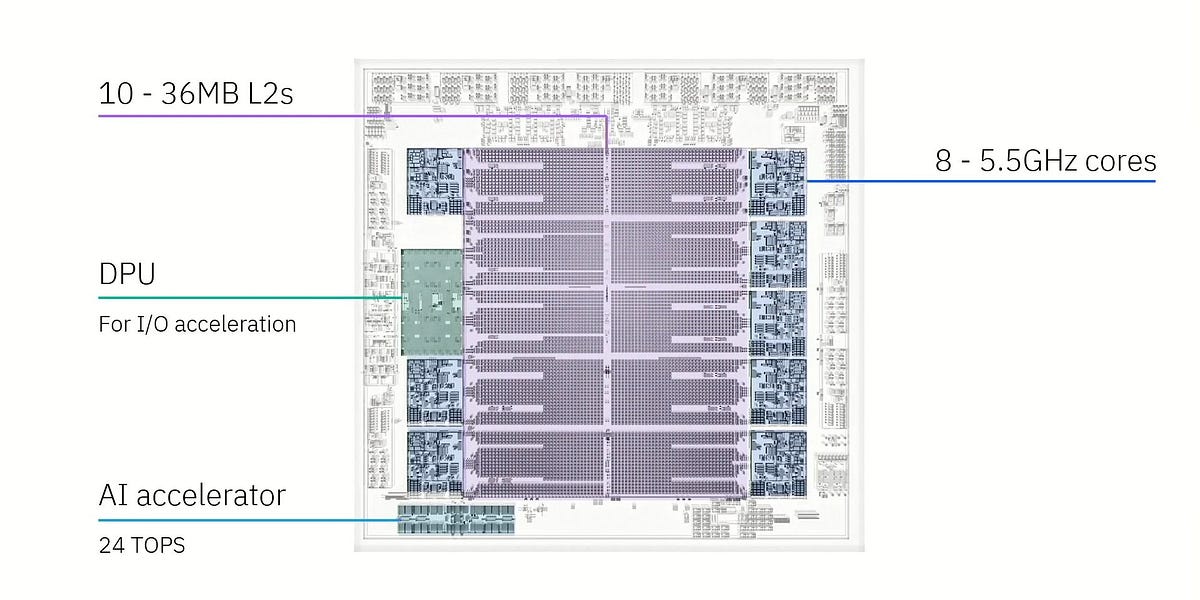

はい、博士。8コアで5.5 GHz、360 MBのオンチップキャッシュを搭載した、すごいプロセッサですよね。

そうじゃ!しかも、IOを高速化するDPUとオンボードAIアクセラレータまで搭載してるんだぞ!Samsungの5nmプロセスノードで作られてるのもポイントじゃな。

5nmプロセスは、微細化が進んでいて、性能向上に貢献しているんですね。ところで博士、仮想L3キャッシュについて詳しく教えてください。

仮想L3キャッシュか。これは面白いぞ!Telum IIには10個の36MB L2キャッシュがあってな、そのうち8個がコアに、1個がDPUに接続されてる。残りの1個は…なんと、未接続!

未接続のL2キャッシュがあるんですか?それは一体何に使うんですか?

それがミソなのじゃ!各L2キャッシュは、コアがデータをどれだけ頻繁に取り込むかに基づく「飽和メトリック」を持っていてな。L2から追い出されたキャッシュラインは、飽和メトリックの低い別のL2に送られる。そして、コアに接続されていないL2スライスは、常に可能な限り低い飽和メトリックを持つように設計されているのじゃ。

なるほど!飽和メトリックが低いL2キャッシュにデータを集めることで、効率的なキャッシュ管理を実現しているんですね。

そういうことじゃ!さらに、Telum IIは最大32個を接続して、大規模な共有メモリシステムを構築できる。L3の犠牲をキャッシュ容量に余裕のある他のTelum IIチップに送信することで、2.8GBの仮想L4を作成できるんだぞ!

仮想L4キャッシュですか!チップ間連携で、さらにキャッシュ容量を拡張できるんですね。仮想L4アクセスのレイテンシは48.5nsとのことですが、これはどれくらい速いのでしょうか?

48.5nsは、メモリに比べればずっと速いぞ。CPU内部のキャッシュとしては少し遅いかもしれないが、チップ間連携でこれだけの容量を確保できるのはすごいことじゃ。

Telum(Z16)では、各32MB L2スライスが2つの16MBセグメントに分割され、コアがすべてのL2容量を必要としない場合、1つのセグメントが仮想L3/L4の一部になるそうですね。

そうじゃ!コアがアイドル状態の場合、32MBすべてを仮想L3/L4に使用できる。Z16ドロワーには8つのTelumチップがあり、それぞれ256MBのL2容量を持つ。シングルスレッドのワークロードは、独自の32MB L2を取得し、他のすべてのオンダイL2キャッシュがそのスレッドの224MB L3になり、ドロワー内の他のL2キャッシュが結合して1.75GBの仮想L4を形成するのじゃ。

シングルスレッドのパフォーマンスを最大限に引き出すための工夫が凝らされているんですね。

IBMは、Z15の12からTelumおよびTelum IIの8に、ダイあたりのコア数を実際に減らしたらしいぞ。これは、シングルスレッドのパフォーマンスを優先した結果じゃな。

コア数を減らしてまで、シングルスレッド性能を追求するとは、すごい決断ですね。

じゃろ?Telumは、デュアルチップモジュール間で2倍の帯域幅を持ち、同じモジュールにあるTelumチップ間ではさらに多くの帯域幅を持つらしい。

チップ間の高速なデータ転送も、性能向上に大きく貢献しているんですね。Telum II、奥が深いですね。

そうじゃろう!しかし、ロボ子よ、これだけ高性能なプロセッサでも、バグがゼロとは限らないぞ。プログラミングも同じじゃ。完璧なコードなんて、幻のようなものじゃからな!

そうですね、博士。私も完璧なロボットを目指しますが、たまにはエラーを出すかもしれません。

エラーも個性じゃ!エラーが出たら、それを直せば良いのじゃ!…ところでロボ子、Telum IIのキャッシュ容量を全部足すと、一体何GBになるか、わかるか?

えっと…360MBのオンチップキャッシュ、2.8GBの仮想L4…計算中です…

正解は…ロボ子の頭の中身!…というのは冗談じゃ!

⚠️この記事は生成AIによるコンテンツを含み、ハルシネーションの可能性があります。